数字电路都是由组合逻辑和时序逻辑组成的。组合逻辑即输出完全取决于当前输入的电路,电路不具有存储能力,而时序逻辑的输出不仅取决于当前的输入,还取决于当前电路的状态(也有可能完全取决于当前电路的状态),当前电路的状态是由历史输入决定的,时序逻辑是具有存储能力的。

时序逻辑可以分为异步时序逻辑和同步时序逻辑,这里的STA也暂时只考虑同步时序逻辑。同步时序逻辑的“状态”变换由时钟来驱动,当时钟事件到来时,电路的状态根据电路当前的状态和当前的输入改变到下一个状态。

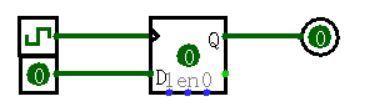

时序逻辑的存储能力由一些具有存储能力的单元提供,例如触发器,这些触发器的存储能力来自于反馈,准确地说是正反馈,在时钟事件没有到来时反馈结构使得时序单元可以保持输出不变,当时钟事件到来时触发器的状态将发生变化,例如下图所示的D触发器:

图1-D触发器

图1-D触发器

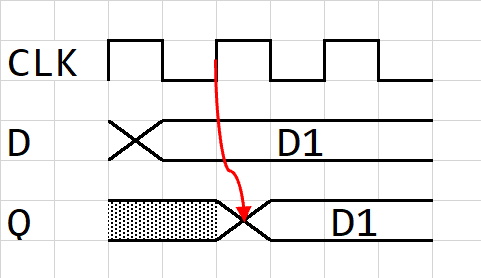

它是边沿敏感的触发器,意思是当时钟沿到来时触发器的状态将发生变化,图中的触发器在时钟的上升沿改变状态,或者说在时钟的上升沿采样输入D。它的状态变化波形如下图所示:

图2-D触发器状态变化波形图

图2-D触发器状态变化波形图

触发器“采样”输入信号需要时间,这个刚采样的值反映到输出也需要时间,这限制了CLK的频率,同时也是电路要进行时序分析(Timing Analysis)的原因之一。我们要知道时钟最快能多快,不能快到还没采旧的数据呢新的数据又来了,也要知道在要采样的时候输入信号得保持稳定多长时间,不能采样还没完成呢输入数据就变了。

STA是静态时序分析(Static Timing Analysis)的简写,这里的静态指的是不需要对电路进行仿真,只需要根据单元的延时信息和相应的约束就可以通过计算来穷举并分析所有需要做时序分析的地方并给出相应的结论。与之相对应的是动态时序分析,这种分析方法需要对电路加以激励并观察电路的行为,虽然更贴近实际应用,但是激励很难覆盖到所有的情况。

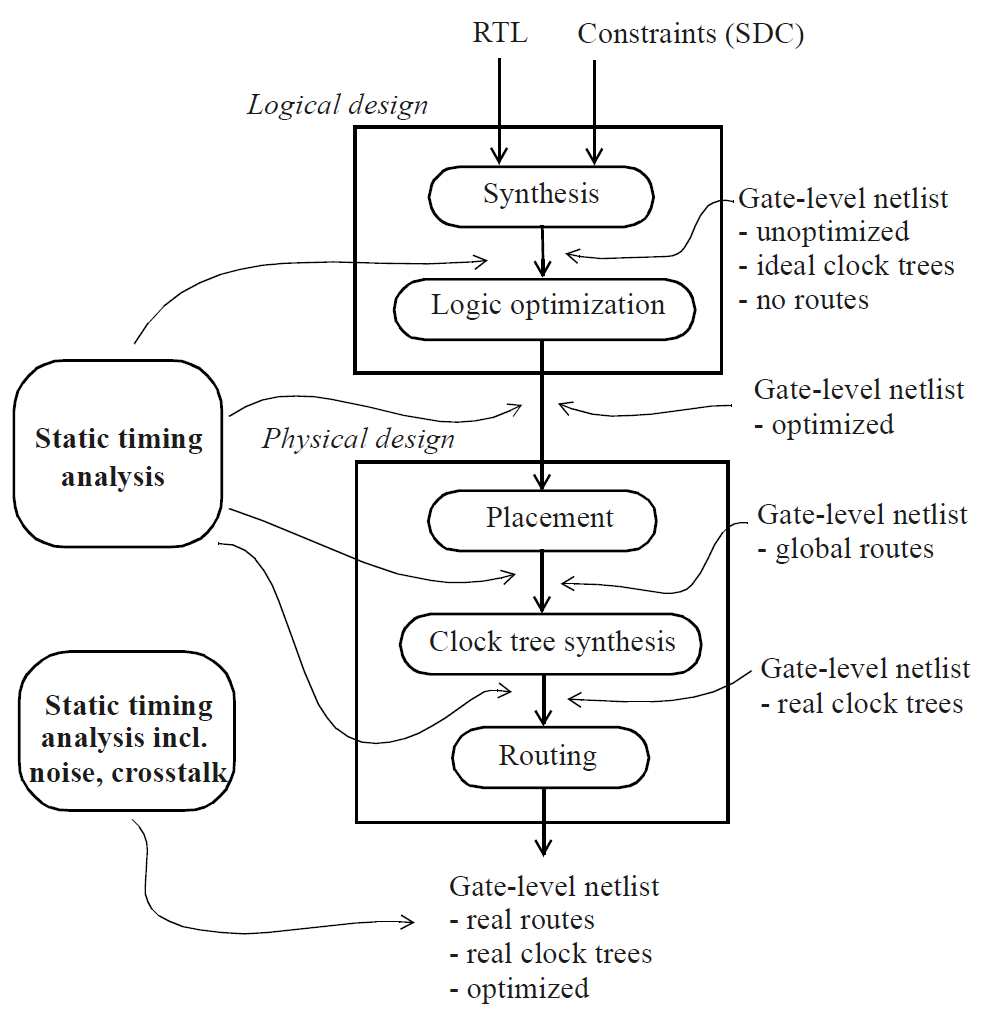

一个典型的数字设计流程如下图所示,其中很多环节都需要做STA

图3-CMOS数字设计流程

图3-CMOS数字设计流程

当然STA并不是万能的,例如它不能处理跨时钟域问题,也不能处理模拟电路和数字电路的接口等等,还是需要结合其他方法来完成,但这些问题不是这一系列博客要讨论的,这里我要总结的是针对同步时序电路的静态时序分析,STA的简介就到这里,下一篇的内容是STA要分析什么,在研究一个问题时当然要先搞清楚我们要研究什么才能下手。

转载请注明来源,欢迎对文章中的引用来源进行考证,欢迎指出任何有错误或不够清晰的表达。可以在下面评论区评论,也可以邮件至 xor0205@163.com